\\\ Silonex NSL32-SR3 ///

"STATIC" Spice Model Derivation

JC Maillet (c) 2008

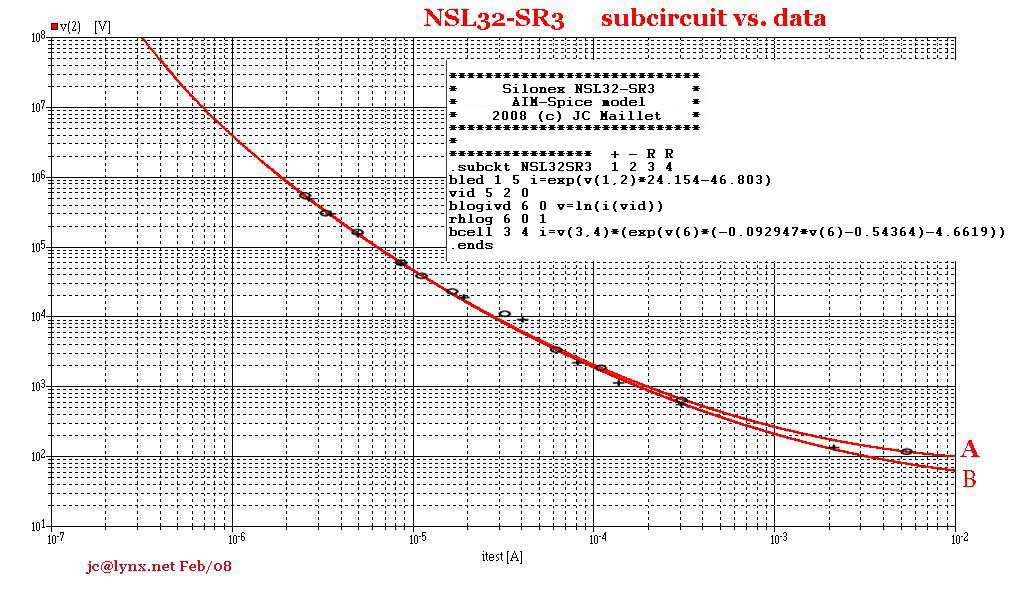

Static Spice modeling means that time dependencies are not factored into the functional derivation, implying the

model is to be considered for accuracy at DC and up to low speeds only (<5Hz) though this is plenty enough for basic functional

and parametric simulations ... there are several potential sources of distortion known to exist with opto-couplers,

one is tell-taled by a very slight bend occuring in the mid-range of a cell's characteristics (see data below), but this usually affects

signal shaping only if the region containing the bend is traversed quickly and repeatably - a most unlikely scenario in most circuits ...

and the other is due to a "memory" effect following an unusually strong burst of light into the cell (causing it to get

stuck before relase) - again, very unlikely if resistance levels are kept well above a certain minima ... this is easy to

design around - especially with the high sensitivity of the SR3 cell ... note that neither form of distortion is included

in this model by nature of the polynomial interpolations ... again, similar to the Triode models I published

in '98, the data gets interpolated more accurately if the data is first linearised by a logarithmic conversion ...

The Silonex NSL32-SR3

opto-isolator/coupler is considered one of the fastest opto-cells on the market and makes it idea for a broad range of

fast and accurate

applications, including local and remote (fibre-optic) control and analogue processing functions and high performance

audio processing blocks (as seen in countless

commercial applications) ... the spec sheet data says it

takes 2.5mS for the cell resistance to roughly triple in value when the LED is

suddenly shut off (free-fall mode) and only 1mS for an inverse thirding when the LED is suddenly turned on (free-float mode) -

this fully describes the timing of the cell aside from the said Memory issue ... I haven't found an ellegant way of

modeling this time dependency yet - I'm not a huge fan of embeded ideal diodes, somebody prove me wrong please ... but of

course a great deal of work can be accomplished with the STATIC model alone so I'm not super hung up on modeling the timing part ...

|

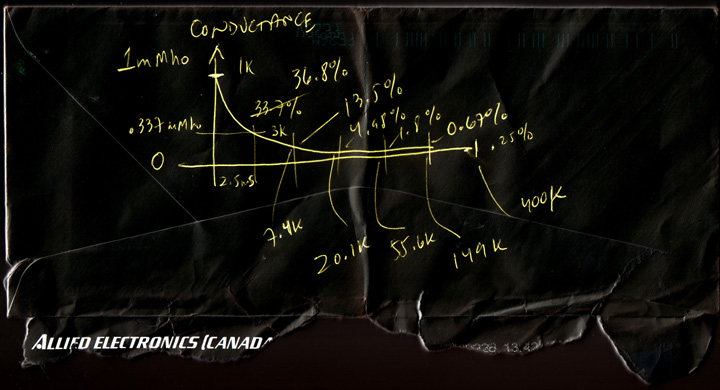

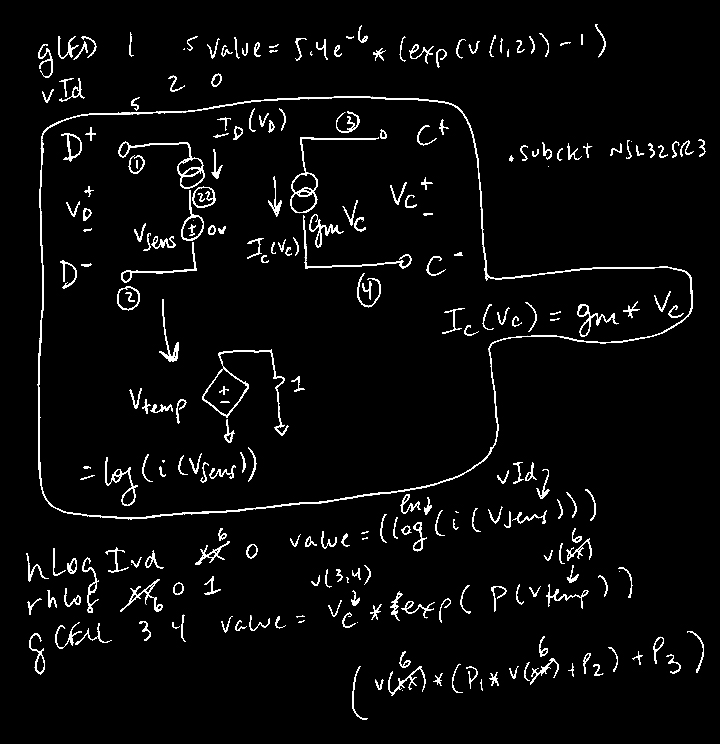

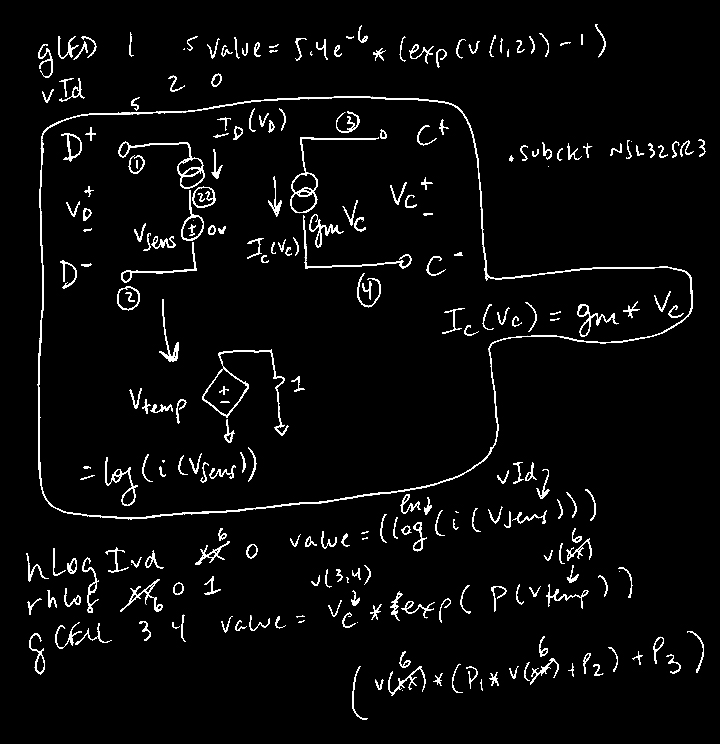

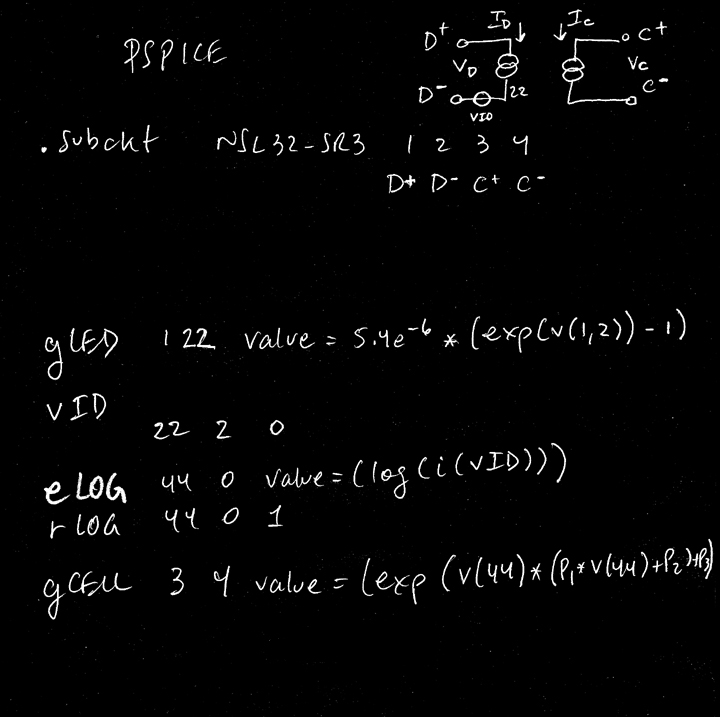

Basic Principle using VCCS and CCCS Controlled Current Sources

-> using Spec-Sheet LED modeling at first

|

Model Breakdown including Log Conversion of Data

|

NSL-SR3 Static Spice Model with Spec-Sheet LED modeling

|

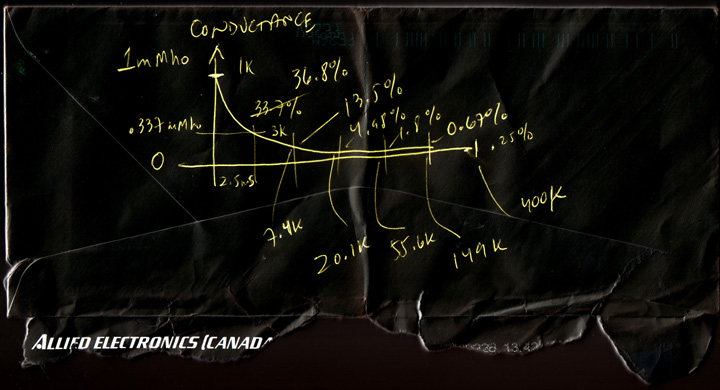

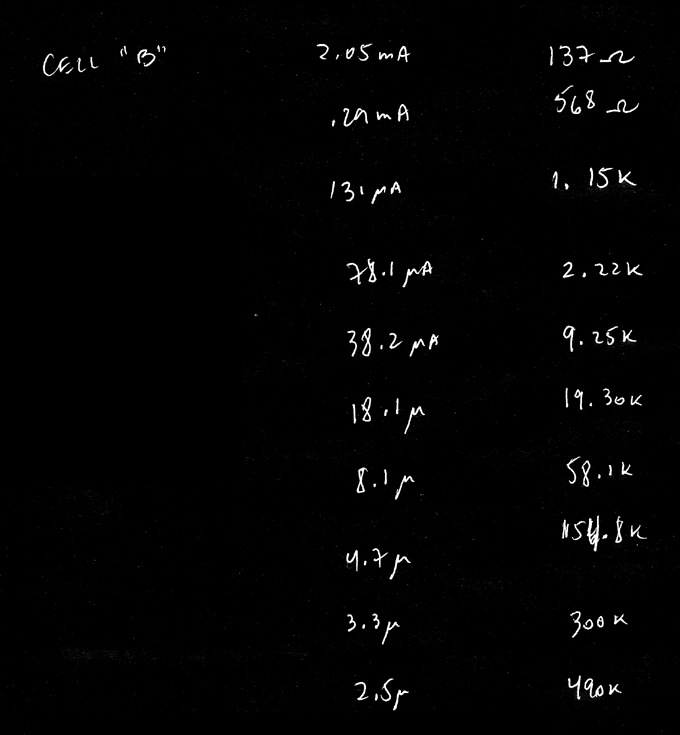

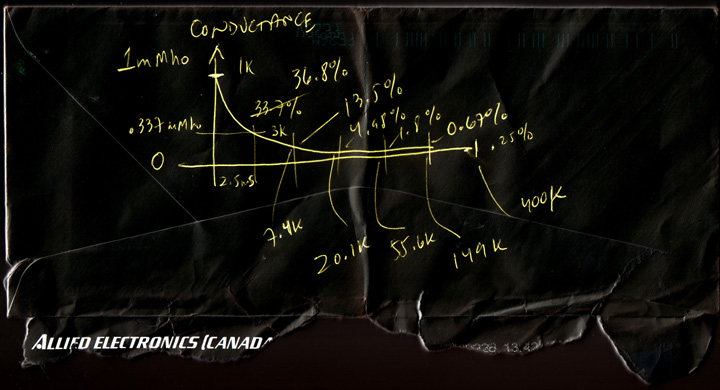

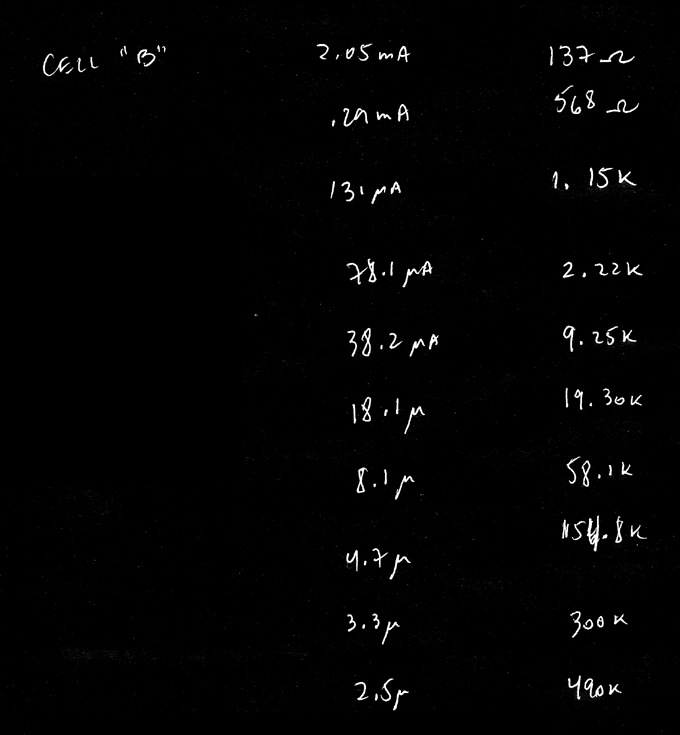

Measured iLed-Rcell Data

|

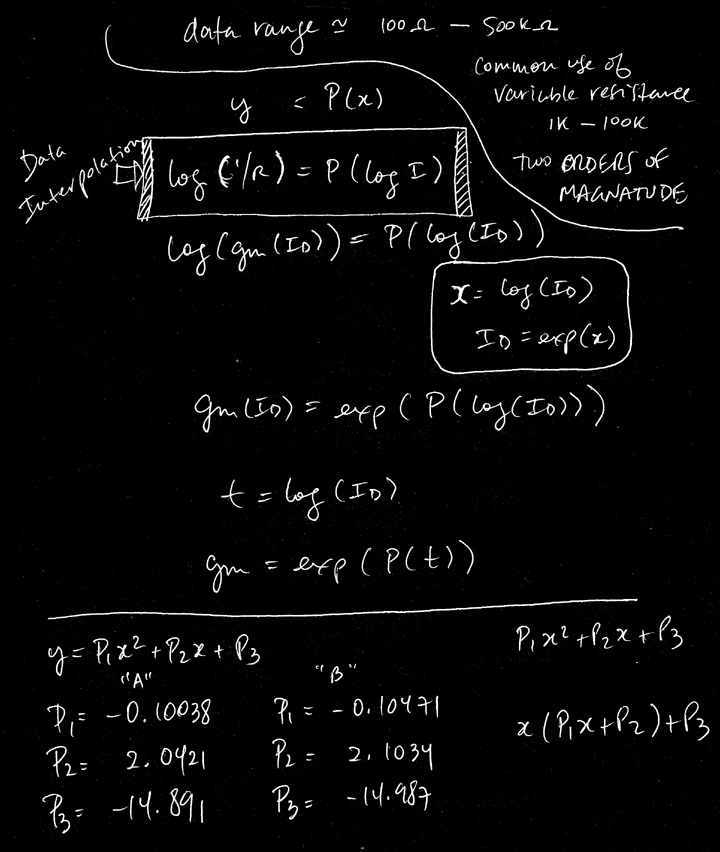

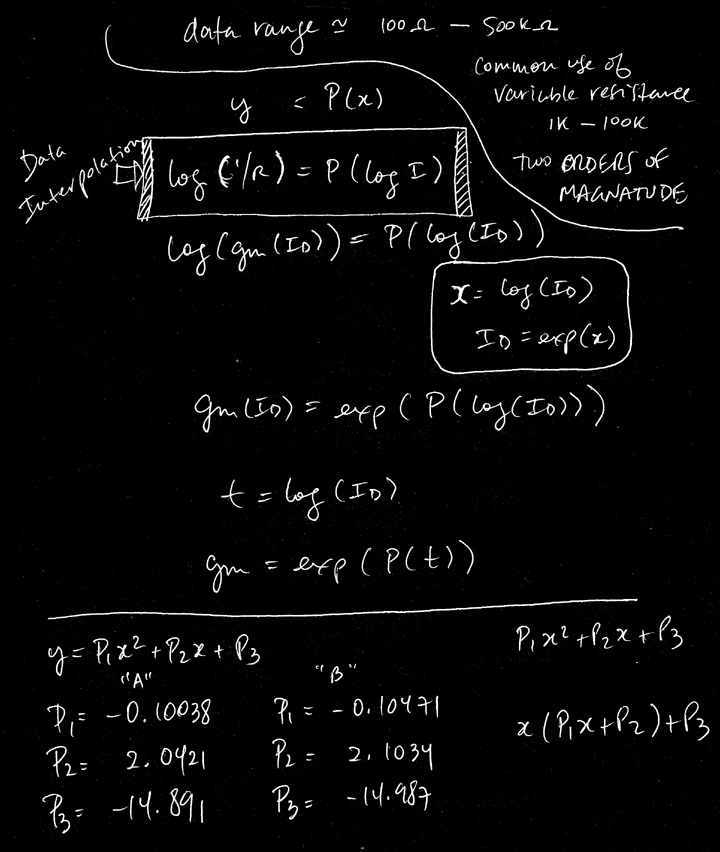

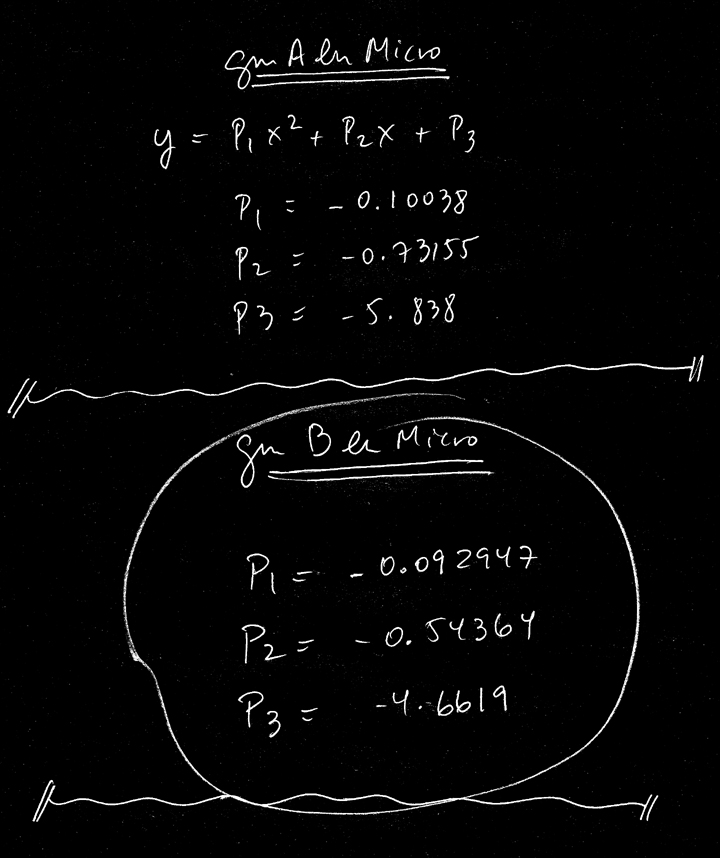

Cell Math with Lin/Log(Final) Data Conversion to ease interpolation

|

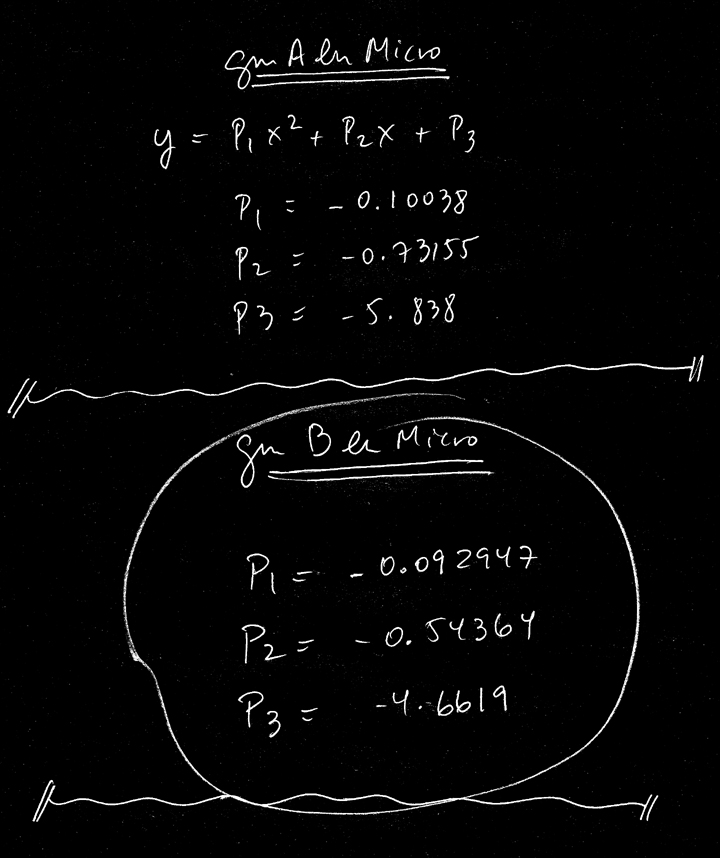

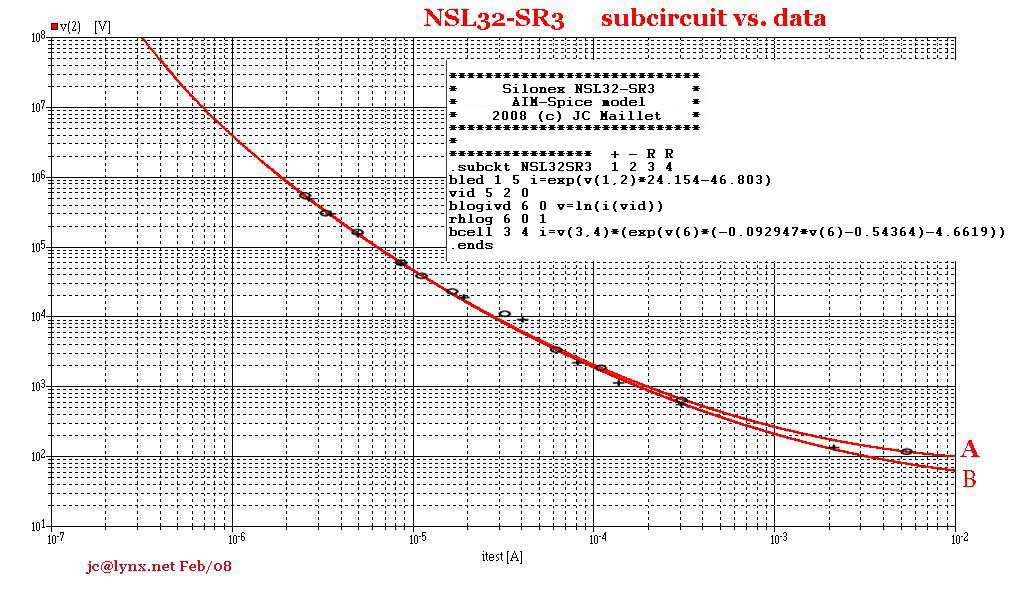

Matlab Interpolation of Log-converted Data

|

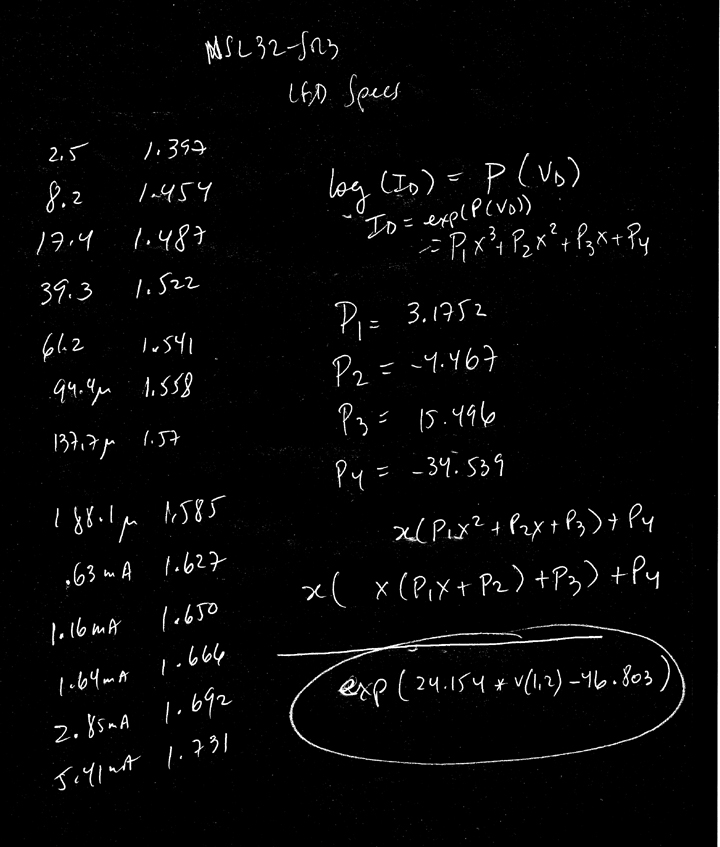

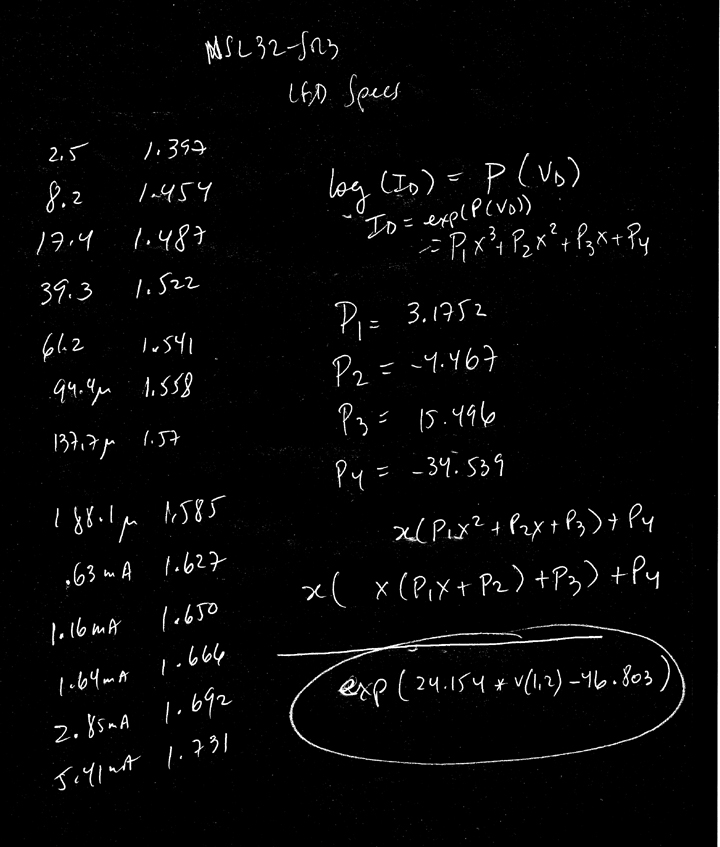

Measured LED V-I Data - 3rd Order and 1st Order (Final) Math

log converted LED Data well approximated by Line - so Data very exp-like as expected

|

Model Output Data Voltage from 1A Cell (test) Current

**LED and Cell Modeling from Measured Data (curve "B" in graph)**

|

HR>

Design spinoffs:

simple and accurate linear-db converter for resistance control of gain

simple low-voltage (3v) optical multi-potentiometer circuitry with stretchable "S" profile

wide range Filters and Gain blocks with sweep Gain and Offset controls

low-noise mute and current-mirror control functions, symmetric bi-oscillator interfacing for stereo anti-phase effects

and a couple more surprises ...

\\\ ** UPDATE 05/2020 ** ////

see here for the latest updates to my NSL32-SR3 modelling efforts :

viva Analog /// jc -> lynx.net